# Pulsonix PCB Layout

## Pulsonix PCB Layout

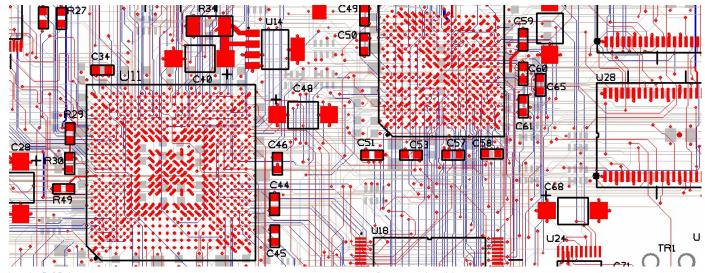

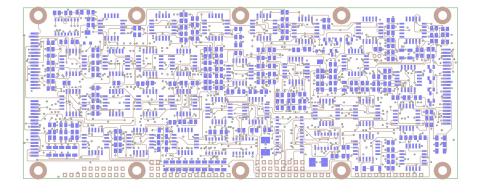

Pulsonix provides an expert design environment to get your boards produced fast with as little effort as possible. With unparalleled ease of use, Pulsonix provides a feature-rich toolset to get the job done efficiently. Everything in Pulsonix is logical, easy to setup and easy to use. Even complex design constraint rules can be easily defined using highly accessible dialogs.

### Technology files for fast start-up

Just like templates used for other desktop products, Pulsonix has a unique system of technology files for fast start-up. Customise and predefine items such as Design rules, Layers, Materials, Spacing rules and Copper/Thermal rules as well as styles for text, tracks, pads, lines to name a few. Company standards can be created in one file then used and shared by all Pulsonix users. Technology files can be created and updated as you design to create a master file containing all your design settings.

#### Import filters

Pulsonix boasts the industry's largest range of import filters. Tried and tested, these are high-quality reliable import filters that have been proven time and time again. Import filters are available for:

| ı               | 0 1                          |              |

|-----------------|------------------------------|--------------|

| ■ Altium        | <ul><li>DxDesigner</li></ul> | Ultiboard    |

| Accel / Protel  | ■ ViewLogic                  | ■ Easy-PC    |

| P-CAD           | ■ Eagle                      | ■ EdWin      |

| ■ CadStar       | ■ Integra                    | ■ CirCAD     |

| ■ Visula PCB    | OrCAD                        | DesignSpark  |

| System Designer | ■ Cadence Allegro            | ■ PCB Artist |

| ■ PADS          | Zuken CR5000                 | ■ Plus more  |

## Construction Lines

Unique to Pulsonix, construction lines provide user-definable 'guide' lines within your design. Use construction lines to create complex board outlines or design items and to align irregular shapes. With their own layer, colour and style, construction lines are valuable for all 2D creation without the need to import complex shapes from outside of your PCB design environment.

#### True Mixed Technology Support

Technology is supported for standard plated through holes, surface mount devices/technologies, blind and buried vias and laser/plasma drilled micro-vias. Pads with slots or non-round holes are easily achieved using standard pad style definitions or custom pad shapes.

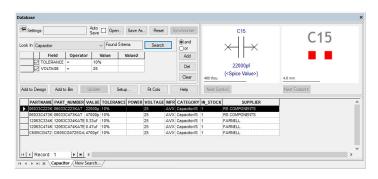

The Pulsonix Database Connection option provides instant access to your Parts database

## Design Variants

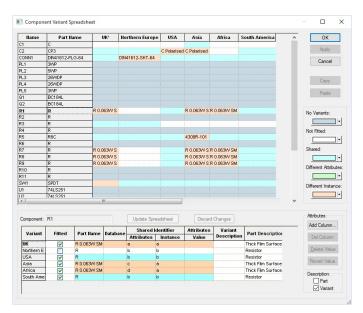

Using the Variant Manager, easily create any number of variants may be defined at either the Schematic or the PCB design stage. If using the Schematic as the master, the variant information will be automatically transferred to the PCB design. Detailed part variants can be easily created. Pulsonix allows Fitted/Not Fitted, different Part, Footprint, Attributes/Values, and even a different number of footprint pins per Component.

### Flexible Interactive Routing Modes

All track shape styles can be changed on-the-fly using the context menu. Change between orthogonal, Angled, Any angle and Curved tracks. Angled tracks can be filleted, blending them between each other. Further blending can be achieved using the teardrop function. Outside of the standard routing modes, Pull Tight is a minimalist mode that enables the shortest track path between the source and target to be achieved. Following the spacing rules and with Online DRC switched on, this is a powerful semi-automatic mode in which to make precise track edits.

Complex assembly variants to match your global customer base

Advanced auto-place and auto-routing algorithms' accelerate your design flow

## Constraint Rules

Define and manage your constraint rules using the Constraint Manager. All rules previously defined in the Schematic editor are seamlessly passed through into the PCB design ready for use. Net Class and Class to Class parameters can be defined for nets where length and spacing rules need to be restricted.

| Rul | es Spreads | heet      |          |             |         |         |            |            |              |          |          |          |             |            |            |             |

|-----|------------|-----------|----------|-------------|---------|---------|------------|------------|--------------|----------|----------|----------|-------------|------------|------------|-------------|

| 4   | Nets       |           | •        | Edit        | Colours | Options |            |            |              |          |          |          |             |            |            |             |

| П   | Net        | Net Class | Bus Name | Sub-Net Att | Pad1    | Pad2    | Min Length | Max Length | Length       | Complete | Max Vias | Num Vias | Min Text Pr | Num Test P | Max Length | Length Diff |

| _   | Diff1      | PAIR      |          |             |         |         | 38.100     | 45.720     | 6.470- Est.  | 177      |          |          |             | 0          | 6.350      | 40.101-     |

| ╗   | HSE1       | HSE       |          |             | Al.     | -       | 8.000      | 24.000     | 19.624+ Est. |          | 1        |          |             | 0          | 2.000      | 29.770+     |

| _   |            |           |          |             | U8.33   | U13.1   | 8.000      | 14.000     | 10.875+ Est. |          | 1        | 0        |             |            |            |             |

| 7   |            |           |          |             | U8.33   | U13.9   | 8.000      | 14.000     | 19.624+ Est. |          | 1        | 0        |             |            |            |             |

| П   |            |           |          |             | U13.1   | U13.9   | 8.000      | 14.000     | 8.749- Est.  |          | 1        | 0        |             |            |            |             |

| П   | HSE2       | HSE       |          |             | A       | _i      | 8.000      | 24.000     | 36.792+ Est. |          | 1        |          |             | 0          | 2.000      | 29.770+     |

| ╗   |            |           |          |             | U8.32   | U13.2   | 8.000      | 14.000     | 10.875+ Est. |          | 1        | 0        |             |            |            |             |

| ╛   |            |           |          |             | U8.32   | U13.8   | 8.000      | 14.000     | 19.297- Est. |          | 1        | 0        |             |            |            |             |

| 7   |            |           |          |             | U13.2   | U13.8   | 8.000      | 14.000     | 29.770+      | 7        | 1        | 2        |             |            |            |             |

| П   | SDLIn_1    | PAIR      |          |             |         |         | 38.100     | 45.720     | 40.101-      | V        |          |          |             | 0          | 6.350      | 40.101-     |

| ı   | SDI In 2   | PAIR      |          |             |         |         | 38.100     | 45.720     | 40.101-      |          |          |          |             | 0          | 6.350      | 40.101-     |

Once design constraints have been defined, view them in real time using the Rules Spreadsheet window

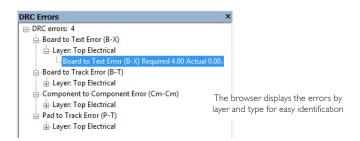

## DFM/DFT

Powerful design rules for manufacturing and test can be defined in addition to Pulsonix' comprehensive set of DRC rules. Following definition, checking is quickly made with all errors and warning displayed in the Errors Rules Panel. Each violation can be easily identified from the sorted list and dynamically reviewed in the design by simply clicking the rule error.

On Pulsonix, high density boards with 8 layers and 0.3mm microvias are being designed as well as power electronics. With an interface to our MCAD system, this has helped us a lot in shortening our development lead-times and is saving the company money.

P. Goerlich, Durr Dental GmbH

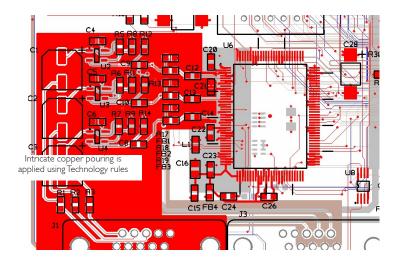

## Copper Pour

Complex copper shapes can be easily created and edited. All Spacing rules, DFM/DFT rules, thermal rules are checked during automatic creation. This produces fast accurate copper areas that are customised to meet your needs. By using the Technology manager, add thermal rules to nets, areas and individual objects. Control over thermal relief on pads is provided for shape, spoke direction, number of spokes and spoke connection status.

## Design Reuse

When designing repetitive circuits Pulsonix provides you with tools to easily copy and replicate existing circuitry from either the current design or a reference design. Using the Autoplace or Layout Pattern facilities, this process is automated and simplified in Pulsonix.

## Powerful Report Writer

The powerful Report Maker feature enables complex reports and netlists to be created using the easy-to-use dialog. ASCII-based Pick and Place reports, interfaces to assembly and manufacturing tools can be created with ease.

#### ECAD-MCAD Co-Design

Bridge your MCAD-ECAD flows and design environments with support for STEP, DXF and IDF. Where a mechanical interface is required, the bi-directional STEP interface can utilise STEP models and import critical board outlines and positional changes. The STEP exporter will write the board outline out ready to add mechanical data. The built-in STEP previewer allows you to examine and verify the design data before you send it to the MCAD system.

Pulsonix has proved to be an excellent choice for Crowcon, enabling us to keep to R&D deadlines. Pulsonix has paid for itself many times over in reduced development times and savings on bureau costs.

A. Beasley, Crowcon Ltd.

## Standard Manufacturing Outputs

Extensive manufacturing outputs are exported - Gerber, Excellon, ODB++,Windows, HPGL, IPC-2581, IPC-356, JTAG, PDF plus a fully customisable Report Maker interface to create company reports, BOMs, netlists and assembly placement outputs as you require.

## FPGA Integration

As standard, Pulsonix is supplied with a built-in FPGA interface that tightly integrated with the Altera Quartus II and Xilinx ISE development systems.

## Pulsonix PCB Layout Summary:

- Design area up to 10.0m by 10.0m (393" by 393")

- Unlimited number of user defined layers

- Via stitching into/around areas and tracks

- Advanced Footprint Rules Technology for manufacturing

- Wizards for: Data Transfer, Footprint creation & Parts creation

- Integrated Autorouter and Autoplace

- On-line and Batch Design Rules Checking (DRC)

- On-line Display Clearances

- Design rules error browser

- View your boards using the built-in 3D Viewer

- Automatic Net Testability and Testpoint Analysis

- Rebuild Gerber files intelligently into design format

- Reverse Engineer, rebuild SCM design from PCB

- Extensive Report outputs including Parts list & BOM

- Dynamic Dimensioning

### **Pulsonix**