Pulsonix FPGA Interface

Pulsonix FPGA Interface

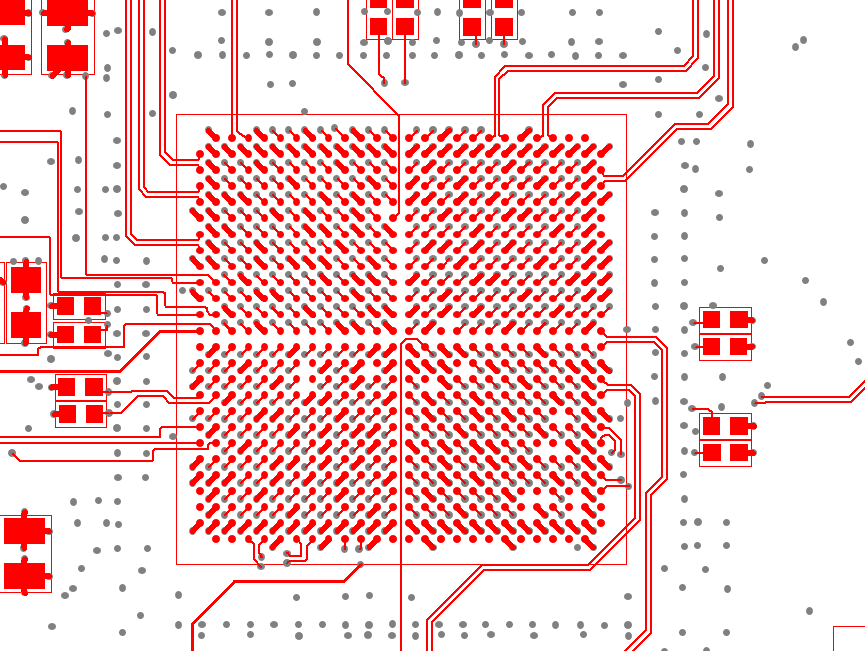

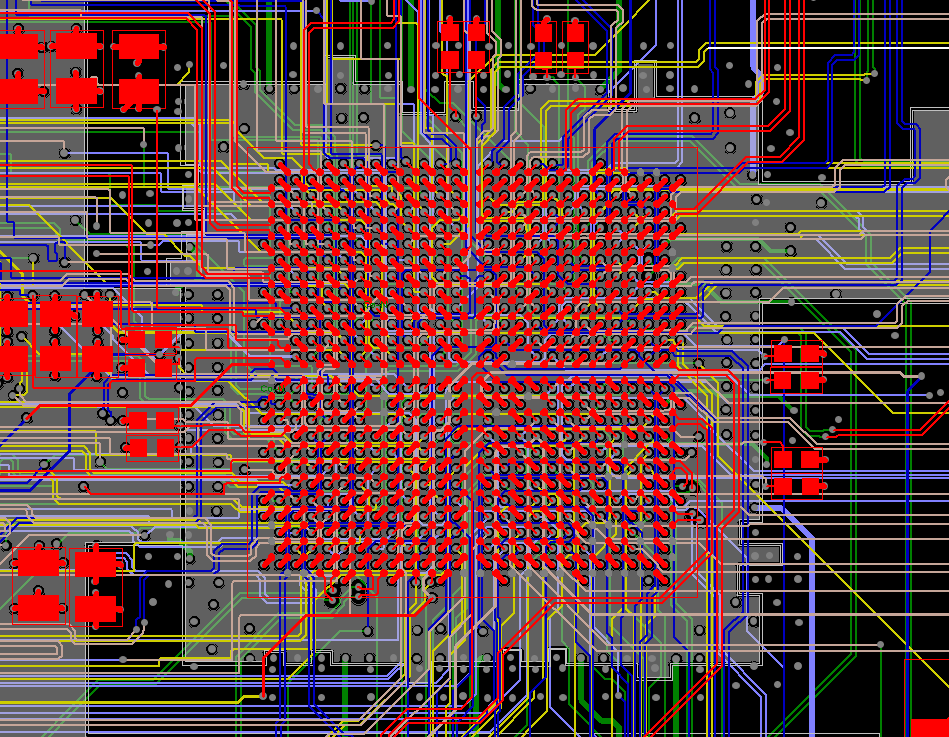

Pulsonix includes features to aid the use and integration of Field Programmable Gate Arrays (FPGA) and the increasing large pin counts associated with this type of device. The FPGA interface is supplied as standard free-of-charge within the Pulsonix Schematic Capture and PCB Design environments.

Most of the major FPGA manufacturers provide their own tools for designing the logic and performing the pin assignments necessary with a FPGA. Interface features are provided to allow the integration of these tools and the data they generate directly into the Pulsonix system. Pulsonix will directly support formats for Altera's Quartus II development system and the Xilinx ISE development system. Additional FPGA system interfaces are scheduled for development. Pulsonix also writes and reads Part Pin CSV format files, this generic format can also be used in the FPGA environment for use with alternative systems.

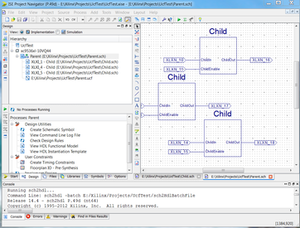

The Process Flow

FPGA pin assignment data generated by manufacturers' tools can be imported into a Part in the Pulsonix

library. You can also start from within the Pulsonix Part editor and export the Part pin data to a CSV

format file for use with the FPGA tool.

FPGA Interface

In parallel, you can develop your FPGA internal functionality using the Altera and Xilinx

development tools. Once completed, or even part completed, export an ASCII file. Changes

to the FPGA pin-out can be quickly reloaded into Pulsonix reducing the need for error prone

manual editing.